## This E-Book and More

### From

http://ali-almukhtar.blogspot.com

## PIC Microcontrollers

# PIC Microcontrollers An Introduction to Microelectronics

**Second Edition**

### Martin Bates

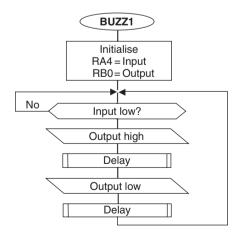

Newnes An imprint of Elsevier Linacre House, Jordan Hill, Oxford OX2 8DP 200 Wheeler Road, Burlington, MA 01803

First published 2000 by Arnold Second edition 2004

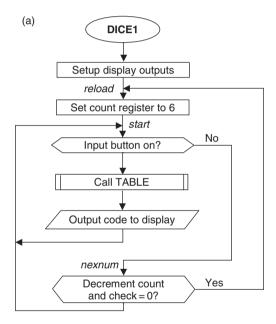

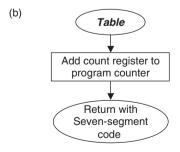

Copyright © 2004, Martin Bates. All right reserved

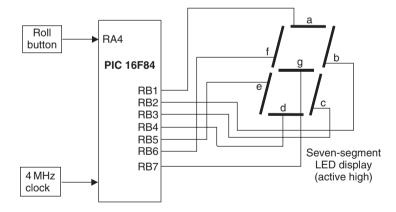

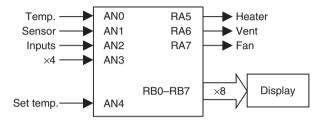

Appendix A has been reprinted with permission of the copyright owner, Microchip Technology Incorporated © 2001. All rights reserved. No further reprints or reproductions may be made without Microchip Technology Inc.'s prior written consent.

Information contained in this publication regarding device applications and the like is intended as suggestion only and may be superseded by updates. No representation or warranty is given, and no liability is assumed by Microchip Technology Inc. with respect to the accuracy or use of such information, or infringement of patents arising from such use or otherwise. Use of Microchip Technology Inc. products as critical components in life support systems is not authorized except with express written approval by Microchip Technology Inc. No licenses are conveyed implicitly or otherwise under any intellectual property rights.

The right of Martin Bates to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988

No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England WIT 4LP. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publisher

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 84830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.co.uk. You may also complete your request on-line via the Elsevier homepage (http://www.elsevier.com), by selecting 'Customer Support' and then 'Obtaining Permissions'

#### **British Library Cataloguing in Publication Data**

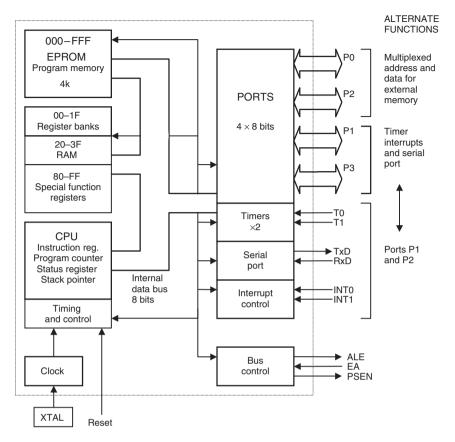

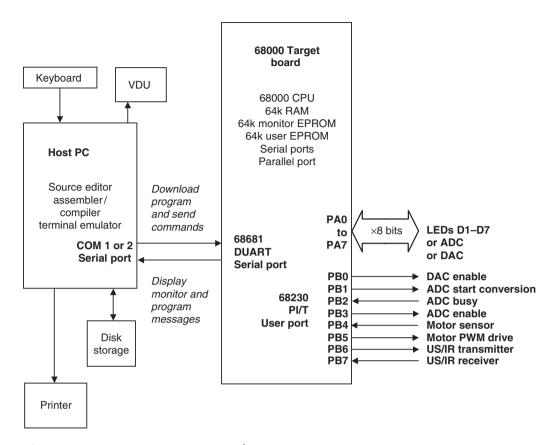

A catalogue record for this book is available from the British Library

#### Library of Congress Cataloguing in Publication Data

A catalogue record for this book is available from the Library of Congress

ISBN 0 7506 6267 0

For information on all Newnes publications visit our website at http://books.elsevier.com

Typeset in 10/12 pt Times by Integra Software Services Pvt. Ltd, Pondicherry, India www.integra-india.com

Printed and bound in Meppel, The Netherlands by Krips bv.

## **Contents**

| Preface to the First Edition |                                                                                                                                                                 | х                                      |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Preface to                   | the Second Edition                                                                                                                                              | xii                                    |

| Introduction                 |                                                                                                                                                                 | xiii                                   |

| PART A                       | MICROELECTRONIC SYSTEMS                                                                                                                                         | 1                                      |

| Chapter 1                    | Computer Systems                                                                                                                                                | 3                                      |

|                              | 1.1 The PC System 1.2 Wordprocessor Operation 1.3 PC Microprocessor System 1.4 PC Engineering Applications 1.5 The Microcontroller Summary Questions Activities | 3<br>9<br>11<br>14<br>15<br>18<br>18   |

| Chapter 2                    | Information Coding                                                                                                                                              | 20                                     |

|                              | 2.1 Number Systems 2.2 Machine Code Programs 2.3 ASCII Code Summary Questions Answers Activities                                                                | 20<br>25<br>28<br>29<br>29<br>30<br>30 |

| ٧i | Contents |

|----|----------|

| Chapter 3 | Microelectronic Devices                             | 32       |

|-----------|-----------------------------------------------------|----------|

|           | 3.1 Digital Devices                                 | 32       |

|           | 3.2 Combinational Logic                             | 36       |

|           | 3.3 Sequential Logic                                | 39       |

|           | 3.4 Data Devices                                    | 41       |

|           | 3.5 Simple Data System 3.6 4-Bit Data System        | 43<br>44 |

|           | 3.6 4-Bit Data System Summary                       | 47       |

|           | Questions                                           | 47       |

|           | Activities                                          | 48       |

| Chapter 4 | Digital Systems                                     | 49       |

| •         | 4.1 Encoder and Decoder                             | 49       |

|           | 4.2 Multiplexer, Demultiplexer and Buffer           | 51       |

|           | 4.3 Registers and Memory                            | 51       |

|           | 4.4 Memory Address Decoding                         | 51       |

|           | 4.5 System Address Decoding                         | 54       |

|           | 4.6 Counters and Timers                             | 55       |

|           | 4.7 Serial and Shift Registers                      | 56       |

|           | 4.8 Arithmetic and Logic Unit 4.9 Processor Control | 57<br>58 |

|           | Summary                                             | 59       |

|           | Questions                                           | 59       |

|           | Answers                                             | 60       |

|           | Activities                                          | 60       |

| Chapter 5 | Microcontroller Operation                           | 61       |

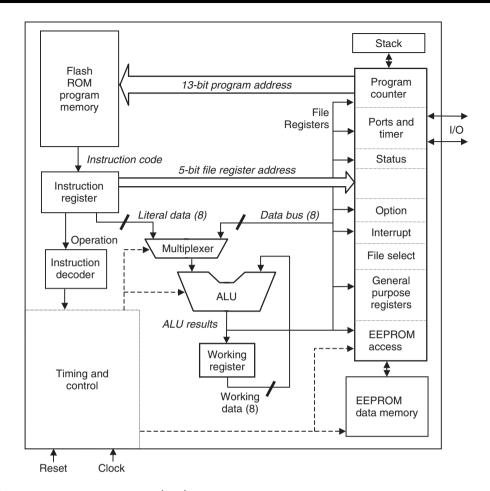

| •         | 5.1 Microcontroller Architecture                    | 61       |

|           | 5.2 Program Operations                              | 65       |

|           | Summary                                             | 73       |

|           | Questions                                           | 73       |

|           | Answers                                             | 74       |

|           | Activities                                          | 75       |

| PART B    | THE PIC MICROCONTROLLER                             | 77       |

|           |                                                     |          |

| Chapter 6 | A Simple PIC Application                            | 79       |

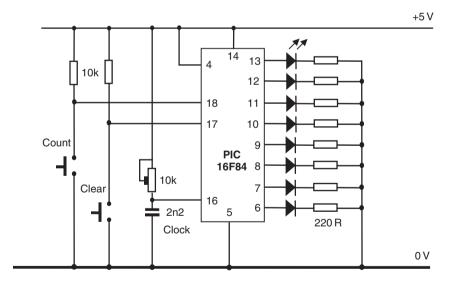

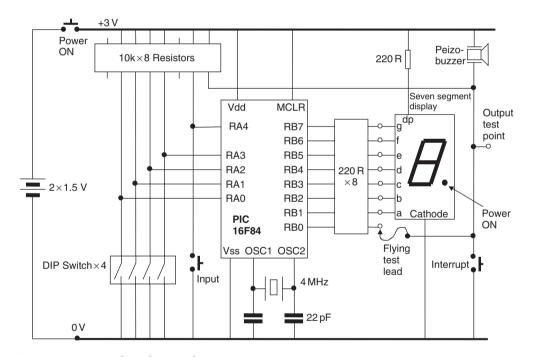

|           | 6.1 Hardware Design                                 | 79       |

|           | 6.2 Program Execution                               | 83       |

|           | 6.3 Program BIN1                                    | 85       |

|           | 6.4 Assembly Language                               | 87       |

|           |                                                   | Contents vii |

|-----------|---------------------------------------------------|--------------|

|           | Summary                                           | 90           |

|           | Questions                                         | 90           |

|           | Answers                                           | 91           |

|           | Activities                                        | 91           |

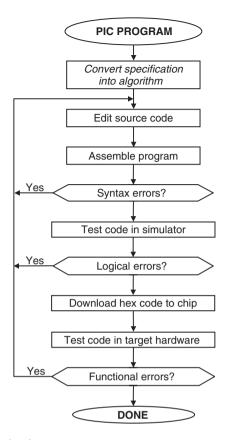

| Chapter 7 | PIC Program Development                           | 92           |

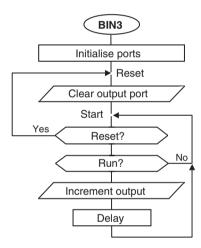

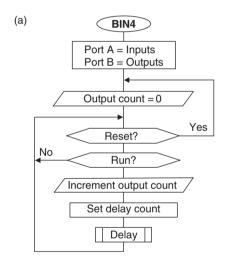

|           | 7.1 Program Design                                | 94           |

|           | 7.2 Program Editing                               | 96           |

|           | 7.3 Program Structure                             | 101          |

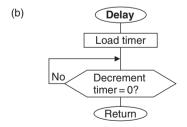

|           | 7.4 Program Analysis                              | 101          |

|           | 7.5 Program Assembly                              | 105          |

|           | 7.6 Program Simulation                            | 109          |

|           | 7.7 Program Downloading                           | 112          |

|           | 7.8 Program Testing                               | 114          |

|           | Summary                                           | 115          |

|           | Questions                                         | 115          |

|           | Answers                                           | 116<br>116   |

|           | Activities                                        | 110          |

| Chapter 8 | PIC 16F84 Architecture                            | 117          |

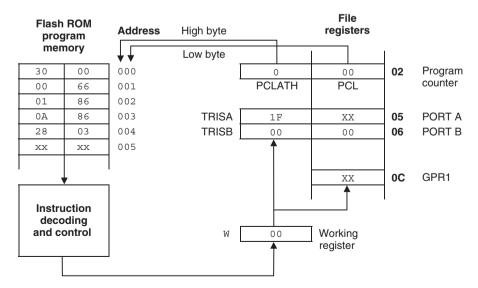

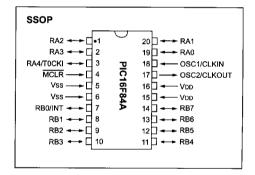

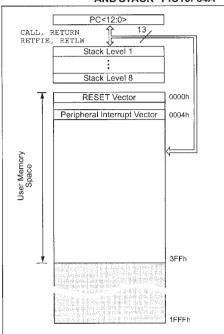

|           | 8.1 Block Diagram                                 | 117          |

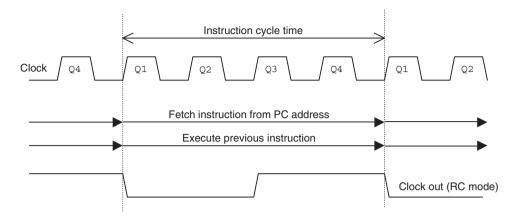

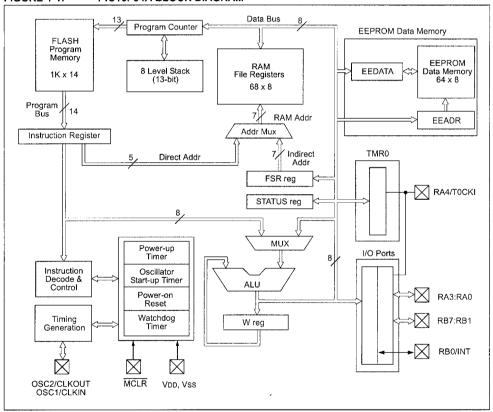

|           | 8.2 Program Execution                             | 119          |

|           | 8.3 Register Set                                  | 120          |

|           | Summary                                           | 126          |

|           | Questions                                         | 127          |

|           | Activities                                        | 127          |

| Chapter 9 | Further Programming Techniques                    | 129          |

| anapioi / |                                                   |              |

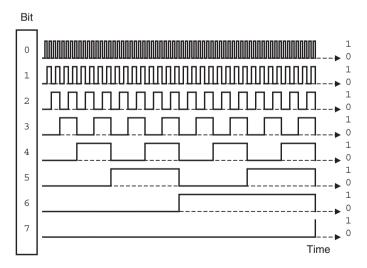

|           | 9.1 Program Timing                                | 129          |

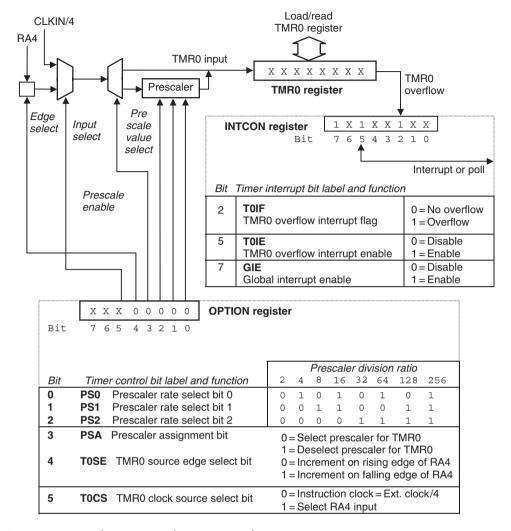

|           | 9.2 Hardware Counter/Timer                        | 131          |

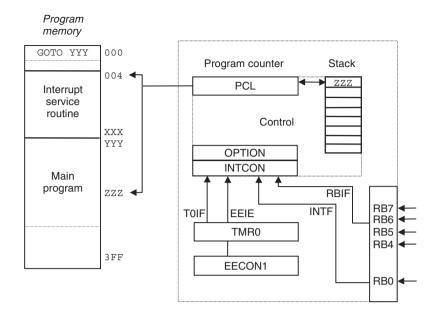

|           | 9.3 Interrupts                                    | 135          |

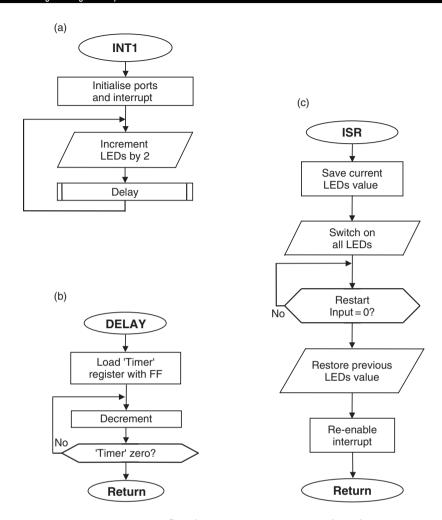

|           | 9.4 More Register Operations 9.5 Special Features | 140          |

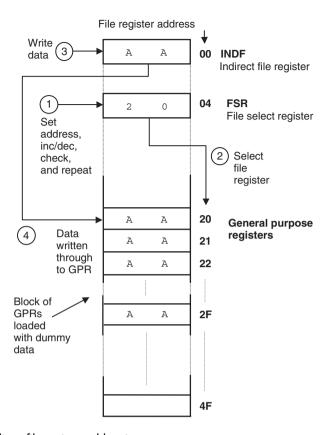

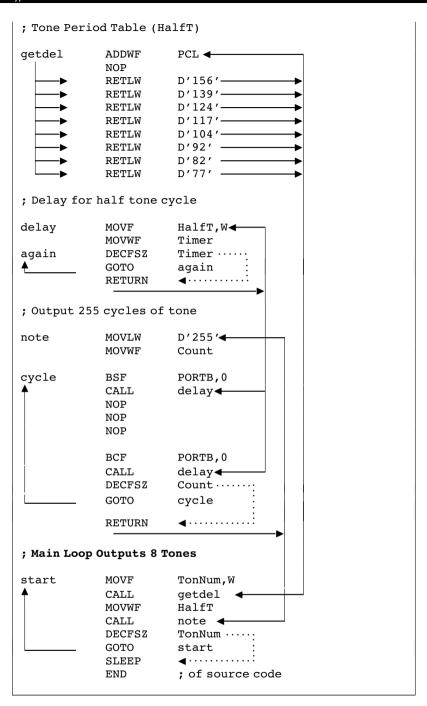

|           | 9.5 Special Features<br>9.6 Program Data Table    | 144<br>148   |

|           | 9.7 Assembler Directives                          | 150          |

|           | 9.8 Special Instructions                          | 153          |

|           | 9.9 Numerical Types                               | 154          |

|           | Summary                                           | 155          |

|           | Questions                                         | 155          |

|           | Answers                                           | 156          |

|           | Activities                                        | 156          |

| viii Contents |                                                                                                                                                                               |                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| PART C        | APPLICATIONS                                                                                                                                                                  | 157                                                  |

| Chapter 10    | Application Design                                                                                                                                                            | 159                                                  |

|               | 10.1 Design Requirements 10.2 Block Diagram 10.3 Hardware Design 10.4 Software Design 10.5 Program Implementation 10.6 Source Code Documentation Summary Questions Activities | 160<br>162<br>162<br>164<br>171<br>174<br>175<br>175 |

| Chapter 11    | Program Debugging                                                                                                                                                             | 177                                                  |

|               | 11.1 Syntax Errors 11.2 Logical Errors 11.3 MPLAB Tools 11.4 Test Schedule 11.5 Hardware Testing Summary Questions Activities                                                 | 177<br>179<br>183<br>184<br>186<br>189<br>189        |

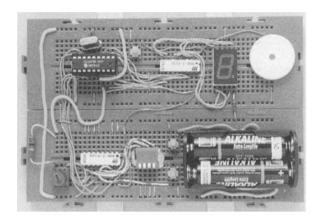

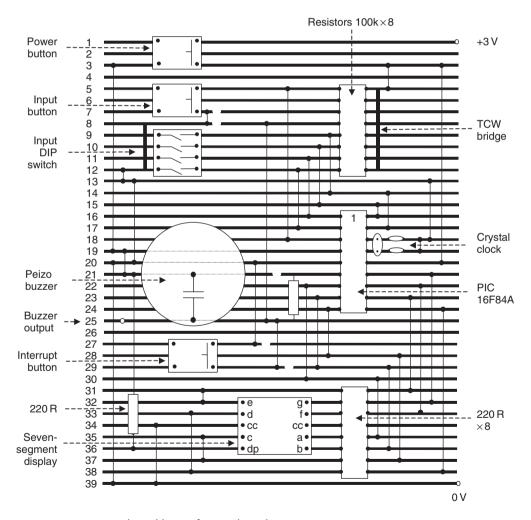

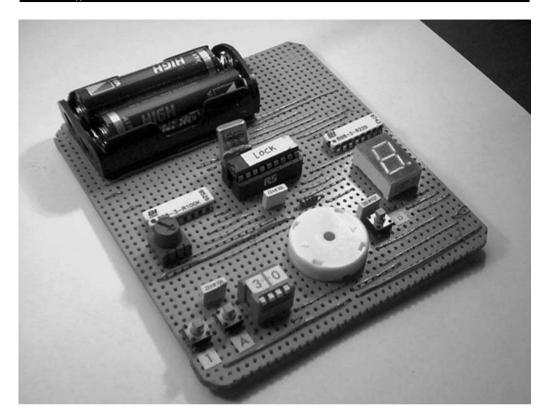

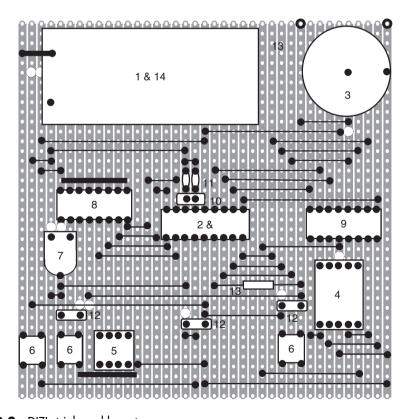

| Chapter 12    | Prototype Hardware                                                                                                                                                            | 191                                                  |

|               | 12.1 Hardware Design 12.2 Hardware Construction 12.3 Demo Board 12.4 Demo Board Applications Summary Questions Activities                                                     | 191<br>192<br>196<br>200<br>210<br>210               |

213

213

214

218

219

221

231

232

232 233

Chapter 13

**Motor Applications**

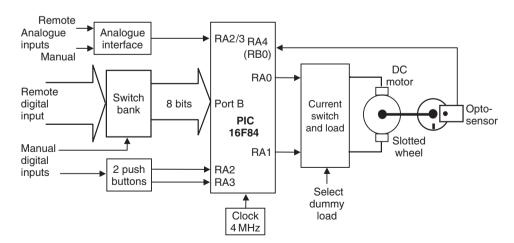

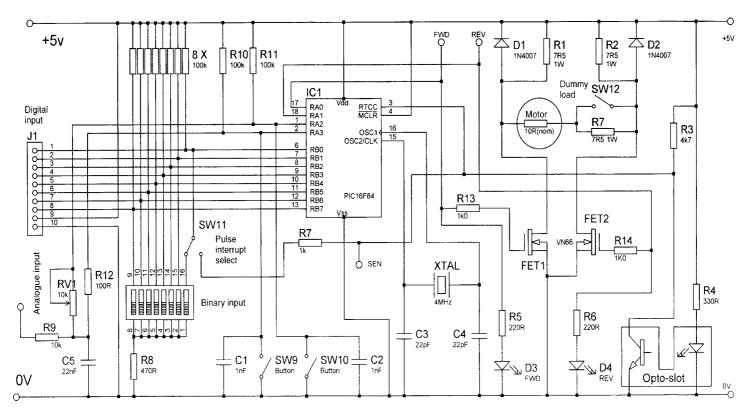

**Motor Control Methods**

**Control Methods**

**Position Control**

**Motor Applications Board**

**Closed Loop Speed Control**

Commercial Application

13.1

13.2

13.3

13.4

13.5

13.6

Summary

Questions

Activities

|            |                                              | Contents ix |

|------------|----------------------------------------------|-------------|

| PART D     | MORE CONTROLLERS                             | 235         |

| Chapter 14 | More PIC Microcontrollers                    | 237         |

| -          | 14.1 Common Features of PIC Microcontrollers | 237         |

|            | 14.2 Selecting a PIC                         | 242         |

|            | 14.3 Advanced PIC Features                   | 244         |

|            | 14.4 Serial Communications                   | 251         |

|            | Summary                                      | 254         |

|            | Questions                                    | 255         |

|            | Activities                                   | 255         |

|            | Answers                                      | 255         |

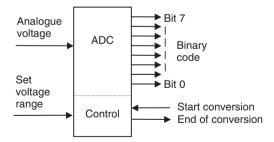

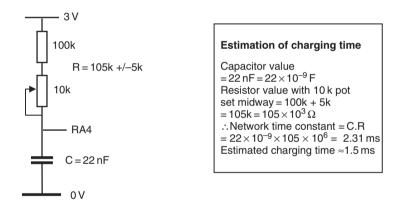

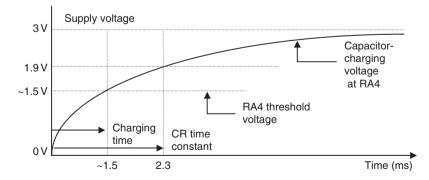

| Chapter 15 | More PIC Applications and Devices            | 256         |

|            | 15.1 16F877 Application                      | 256         |

|            | 15.2 16F818 Application                      | 273         |

|            | 15.3 12F675 Application                      | 274         |

|            | 15.4 18F452 Application                      | 27.5        |

|            | Summary                                      | 278         |

|            | Questions                                    | 278         |

|            | Answers                                      | 279         |

|            | Activities                                   | 279         |

| Chapter 16 | More Control Systems                         | 280         |

|            | 16.1 Other Microcontrollers                  | 280         |

|            | 16.2 Microprocessor System                   | 282         |

|            | 16.3 Control Technologies                    | 288         |

|            | 16.4 Control System Design                   | 298         |

|            | Summary                                      | 299         |

|            | Questions                                    | 301         |

|            | Activities                                   | 301         |

| Appendix A | PIC 16F84 Data Sheet                         | 302         |

| Appendix B | DIZI-2 Board and Lock Application            | 347         |

| Index      |                                              | 367         |

| IIIUUA     |                                              | 30/         |

## Preface to the First Edition

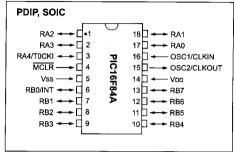

The Microchip<sup>TM</sup> PIC 16F84 microcontroller is an unremarkable looking 18-pin chip – so why write a whole book on it? The answer is that it contains within its ordinary looking plastic case most of the technology that students of microelectronics need to know about in order to understand microprocessor and computer systems. It also represents a significant new development in microelectronics and, importantly, it offers an easier introduction to the world of digital processing and control than conventional microprocessors. The microcontroller is a self-contained, programmable device, and the student, hobbyist or engineer can put it to use without knowing in too much detail how it works. On the other hand, we can learn a great deal about microelectronics by looking inside.

Studying the PIC chip will give the user a valuable insight into the technology behind the explosion in microprocessor-controlled applications which has occurred in recent years, which has been based on cheap, mass-produced digital circuits. Mobile phones, video cameras, digital television, satellite broadcasting and microwave cookers – there are not many current electronic products which do not contain some kind of microprocessor. Industrial control systems have seen similar developments, where complex computer control systems have steadily increased productivity, quality and reliability. The key, of course, is the increase in power of microprocessors and related technology, while the cost of these clever little chips continues to fall.

The microcontroller is essentially a computer on one chip, which can carry out a complex programmed sequence of actions, with the minimum of additional components. As an example, in this book a motor control circuit will be described which allows the motion of a small dc motor to be programmed and controlled by the PIC chip. The only additional major components required are power transistors to provide the current drive to the motor. In the past, equivalent control and interface circuits for such an application would have required many more components, and been much more complicated and expensive to design and produce. The small microcontroller also makes it easier for a device such as a motor to be individually controlled as part of a larger system.

When I first came across the PIC chip a few years ago, it was immediately obvious that this would be an ideal device for teaching and learning microprocessor software techniques, especially for students with minimal prior knowledge and skills. It is relatively cheap, and, even better, it has non-volatile program memory that is electrically reprogrammable (Flash ROM). In addition, the manufacturers, Arizona Microchip, had the foresight to make development system software required to develop programs for the chip widely available. Packages are available for DOS and Windows, and the support hardware and software are being added to all the time, by the manufacturers, independent suppliers and enthusiasts. On the other hand, a complete set of more powerful development tools is also available for the professional user.

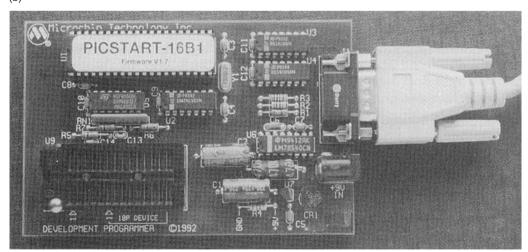

Both DOS and Windows versions of the PIC development system have been used to prepare the sample applications in this book, and the programs downloaded using the PICSTART-16B programming unit. However, there are many designs for inexpensive programmers available in magazines and on the Internet, usually with their own software. The current Windows version of the program development package, MPLAB, can be downloaded free of charge from the Internet at 'http://www.microchip.com', along with data sheets and all the latest product development information. The data sheet for the PIC 16F84 is reprinted in full, because it is an excellent document which contains the definitive information on the chip, presented in a clear and concise manner.

The objective of this book is to ensure that any beginner, student or engineer, will quickly be able to start using this chip for their own projects and designs. When I started using it in my teaching, I put together a teaching pack and was expecting a range of suitable reference books to quickly appear. Indeed, the chip soon started to feature in numerous electronics magazine projects and was clearly popular, but all the books that I obtained seemed to assume quite a lot of prior knowledge of microprocessors. I wanted to use the PIC with students who were new to the subject, and eventually I realised that if I wanted a suitable book, I would have to do it myself! I hope that the reader finds the result useful.

> Martin P. Bates Lecturer in Microelectronics Hastings College of Arts & Technology July 1999

## Preface to the Second Edition

The revisions required in the second edition of this book are mainly due to the rapid development of microcontroller technology. As the PIC family of devices has grown, more features have been incorporated at lower cost. So, while the focus of the first edition was the popular 16F84 chip, and this remains a valuable reference point for the beginner, the scope has been expanded so that a broader understanding of the range microcontroller types and applications can be gained.

One of the reasons the 16F84 was originally selected was its flash memory, which allows easy reprogramming, making it a good choice for education and training. Flash memory is now available in a wider range of devices, making the choice of chip less obvious. On the one hand we now have more small 8-pin chips which can be used in simple systems requiring fewer inputs and outputs, as well as a proliferation of more powerful devices incorporating a variety of serial data interfaces, as well as analogue inputs and many other advanced features.

For this reason the focus has been shifted away from the 16F84. A wider selection of devices and I/O methods is now discussed, and a more general treatment attempted. Application development software has also moved on, and new methods of programming and debugging introduced. I hope I have been able to reflect these developments adequately without introducing too many complications for the beginner, to whom this text is still firmly addressed.

Part A is a general introduction to microelectronics system technology, and can be skipped if appropriate. In Part B, the PIC microcontroller is described in detail from first principles. Part C contains practical advice on implementing PIC projects, with examples. Part D contains new material on the more advanced features of other PIC MCUs (Microcontroller Units) as well as a review of a range of other control system technologies.

I have tried to incorporate a systematic approach to project development, making the design process as explicit as possible. The book will thus support the delivery of the microelectronic systems and project modules of, for example, UK BTEC electronics programmes which incorporate an Integrated Vocational Assignment, which requires the student to develop a specific project and document the process in detail. The PIC is a good choice for producing interesting, but achievable, projects which incorporate a good balance between hardware and software design, and allow the design process to be clearly documented through every stage.

Acknowledgement is due to Microchip Technology Inc. for their kind permission to reproduce the PIC 16F84A data sheet, to Microsoft Corporation and Labcenter Electronics for the application software used to produce documents, drawings, circuit schematics and layouts for this book, and to all for use of their trademarks.

Finally, thanks to the following for their help, advice and tolerance: Melvyn Ball (Hastings College), Jason Guest (General Dynamics, Hastings), Chris Garrett (University of Brighton) and, of course, Julie at home; also, to all colleagues who commented on the first edition, and students who bought it!

Martin Bates December 2003 mbates@hastings.ac.uk

## Introduction

Let's admit one thing straight away – microprocessor systems are quite complicated! However, they are now found in so many different products that all students of engineering need to know something about how they work.

In this book we are going to look specifically at the PIC family of microcontrollers. Microcontrollers have all the essential features of a full-size computer, but all on a single chip. By contrast, conventional microprocessor systems, such as the PC (personal computer), are built with a separate processor, memory, input and output chips. The extra hardware and software required to make these chips work together makes the system more difficult to understand than our single chip microcontroller unit (MCU).

As well as being easier to understand, microcontrollers are important because they make electronic circuits cheaper and easier to build. 'Hard-wired' circuits can be replaced with a microcontroller and its software, reducing the number of components required. Importantly, the software element (control program) can be reproduced at minimal cost, once it has been created. So the development costs may be higher, but the production costs will be lower in the long run. It is also easier to change software if the product is to be modified. In general, software is increasingly replacing hardware in electronic designs. For example, to design a system like a video recorder without microprocessors or microcontrollers would be very complicated and expensive, if not impossible.

Using the PIC, we will find that we can quite quickly work out some simple, but useful, applications. These will illustrate the universal principles of microprocessor systems that apply to more complex computer and control systems. At first, however, we do not have to worry too much about exactly how the chip works – we will go back to that later. The big problem with microprocessors and microcontrollers is that in order to fully understand how the system works, we have to understand both the hardware and the software at the same time. Therefore we have to circle round the subject, looking at the system from different angles, until a reasonable level of understanding is built up.

We will approach microcontroller and microprocessor systems (microsystems) step by step, assuming very little prior knowledge. The operation of the PC will be outlined first, because most students will be familiar with how it works from the user's point of view. We will look at how the hardware and software interact, and the function of the Pentium microprocessor in controlling the input (keyboard, mouse), output (screen) and memory and disks.

Some basic microelectronic system principles will then be covered. One objective is to understand the hardware diagrams in the PIC data sheets, so that external circuits connected to the PIC input/output pins can be designed correctly. Also, it is necessary to understand the internal hardware configuration of a microcontroller to fully understand the programming of the chip. The clarity and completeness of these data sheets is an important reason for choosing the PIC as our typical microcontroller. We can then start to look specifically at the PIC microcontroller and develop simple applications which will illustrate the essential hardware

#### xiv Introduction

features and basic programming ideas. More details will then be added using further application examples.

In the final section, the complete application design process will be described, including use of the PIC development system and hardware design methods. The range of PIC microcontrollers and the more advanced features of some of them will then be described, plus some other types of control technologies which can carry out similar functions to microcontrollers, such as programmable logic controllers.

All reference material can be downloaded from www.microchip.com and other manufacturers' websites.

## Part A Microelectronic Systems

- 1 Computer Systems

- 2 Information Coding

- 3 Microelectronic Devices

- 4 Digital Systems

- 5 Microcontroller Operation

## **Chapter 1**Computer Systems

- 1.1 The PC System

- 1.2 Wordprocessor Operation

- 1.3 PC Microprocessor System

- 1.4 PC Engineering Applications

- 1.5 The Microcontroller

We will begin our study of microsystems with something familiar, by looking at how the PC (personal computer) works when running a wordprocessor. Most readers will be familiar with using a wordprocessor and will know more or less how it functions from the user's point of view. Some basic microsystem concepts will be introduced by analysing how the software operates with the computer hardware, to allow the user to enter, store and process documents. For example, we will see why different kinds of memory are needed to support the system operation.

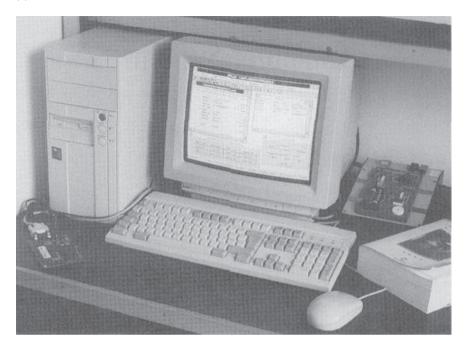

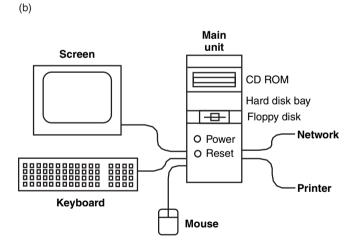

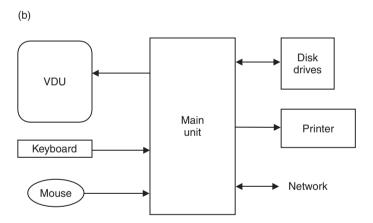

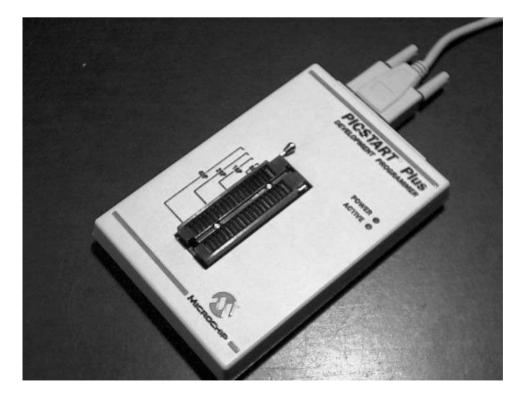

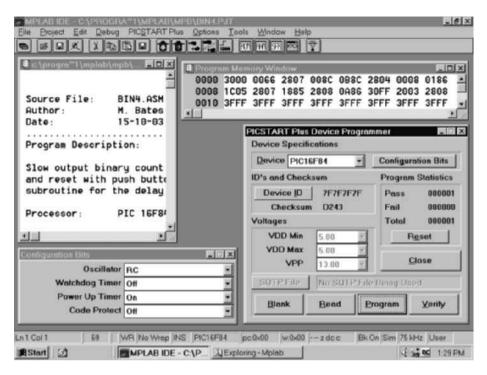

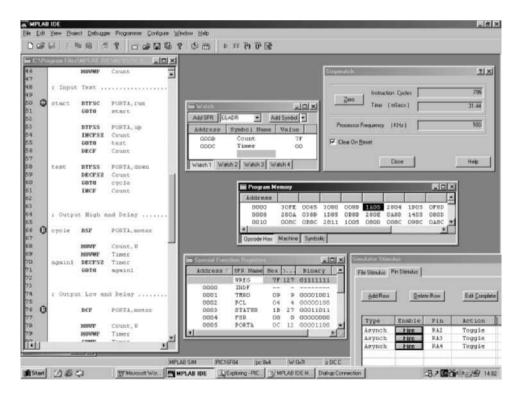

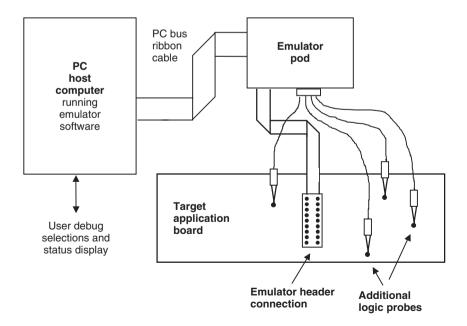

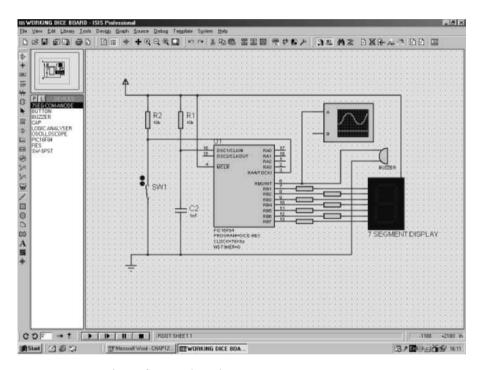

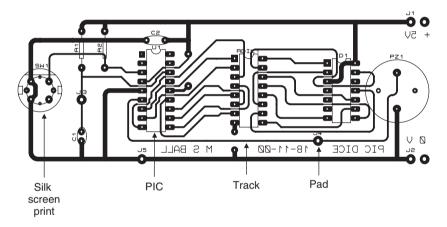

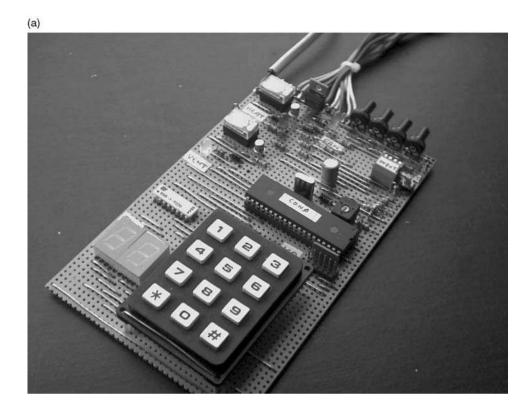

It is also useful to get some idea of how a PC works because it is used as the hardware platform for the PIC program development system. The programs for the PIC are written using a text editor, and the machine code program created and downloaded to the PIC chip using the PC. The PIC development system hardware can be seen connected to the PC in Fig. 1.1(a). A simplified diagram, Fig. 1.1(b), allows us to see the main parts of the system more clearly.

We will then have a quick look at a microcontroller system, set up to operate as a simple equivalent of the microprocessor-based PC system, so we can see how it compares. The microcontroller has a keypad with only 12 keys instead of a keyboard, and a seven-segment display instead of a screen. Its memory is much smaller than the PC, yet it can carry out the same basic tasks. In fact, it is far more versatile; the Pentium<sup>TM</sup>processor used in the PC is designed specifically for that system. The microcontroller can be used in a great variety of circuits. Also, it is much cheaper!

#### 1.1 The PC System

The PC hardware is based on the Intel<sup>TM</sup> series of microprocessors with Microsoft Windows<sup>TM</sup> operating system software. The standard PC hardware comprises a main unit, separate keyboard and mouse, VDU (visual display unit) and possibly a printer and connection to a network. The circuit board (motherboard) in the main unit carries a group of chips which work together

(a)

Figure 1.1 (a) The PC system (with PIC development system); (b) Diagram of PC system.

to provide digital processing of information and control of input and output devices. A power supply for the motherboard and the peripheral devices is included in the main unit.

The processor must have access to software (programs) to allow useful work to be done by the hardware. These are usually stored on a hard disk inside the main unit; this can hold large amounts of data which is retained when the power is off. There are two main types of software required – the operating system (Windows<sup>TM</sup>) and the application (Word<sup>TM</sup>). As well as the operating system and application software, the hard disk stores the data created by the user (document files). Documents can also be stored on floppy disk for backup or portability.

The keyboard is used for data input, and the VDU displays the resulting document. The mouse provides an additional input device, allowing operations to be selected from menus or by clicking on icons and buttons. This is called the graphical user interface (GUI). There may be a network card fitted in the PC to exchange information with other users, download data or applications, or share resources such as printers over a local area network (LAN). In addition, a modem can give direct access to a wide area network (WAN), usually the Internet. A CD ROM drive allows large volumes of reference information stored on optical disk to be accessed, and is also used to load application software.

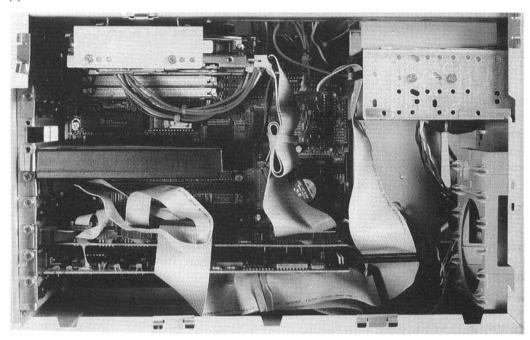

If we remove the cover from the main unit, the main components can be identified fairly easily. In the photograph, Figure 1.2(a), the power supply is top left, with the hard disk drive below and the motherboard vertical at the back of the tower case. The disk and video interface cards are visible at the bottom, slotted via edge connectors into the motherboard, with a modem in the middle in the dark casing. The connections to the video board and modem are available at the rear (left) of the case, with the floppy disk at the front (top right). In current PC designs, some of these interfaces are built into the motherboard, so the whole package is more compact.

Block diagrams are useful for showing the main parts of a complex system, and how they connect together, in a simplified form. Figure 1.2(b) shows the components of the PC system and the direction of the information flow between them. In the case of the disk drives and network it is bidirectional (flowing in both directions), representing the process of saving data to, and retrieving data from, the hard disk or floppy disk.

#### 1.1.1 PC Hardware

Inside the PC main unit, the motherboard has slots for expansion boards and memory modules to be added to the system. The power supply and disk drives are fitted separately into the main unit frame. The keyboard and mouse interfaces are usually on the motherboard. In older designs, the expansion boards carried interface circuits for the disk drives and external peripherals such as the display and printer, but these functions now increasingly incorporated into the motherboard itself. Note that the functional block diagram does not show any difference between internally and externally fitted peripherals, because it is not relevant to the overall system operation.

The PC is a modular system, which allows the hardware to be put together to meet the individual user's requirements, and allows subsystems, such disk drives and keyboard to be easily replaced if faulty. The modular design also allows upgrading (for instance, fitting extra memory chips) and also makes the PC architecture well suited to industrial applications. In this case, the PC can be 'ruggedised' (put into a more robust casing) for use on the factory floor. This modular architecture is one of the reasons for the success of the PC as a universal hardware platform.

#### 1.1.2 PC Motherboard

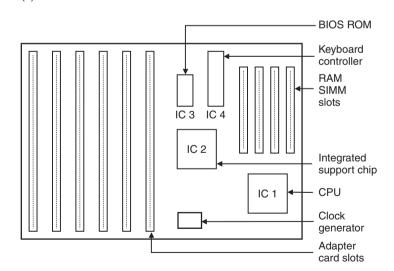

The main features of a typical motherboard are shown in Fig. 1.3. The heart of the system is the microprocessor, a single chip, which is also called the central processing unit (CPU). This name refers back to the days when the CPU was built from discrete components and could be the size of a washing machine! In Fig. 1.3(a), the CPU is under the cooling fan at the lower right. The CPU controls all the other system components, but must have access to a suitable program in memory before it can do anything useful. The blocks of program required are provided by the operating system software and the application software which are downloaded to memory from the hard disk on startup.

(a)

Figure 1.2 The PC system main unit. (a) View of PC main unit; (b) Block diagram of PC system.

The Intel CPU has undergone continuous development since the introduction of the PC in 1981, with the Pentium processor being the current standard. Intel processors are classified as CISC (complex instruction set computer) devices, which means they have a relatively large number of instructions which can be used in a number of different ways. This makes them powerful, but relatively slow compared with more streamlined processors which have fewer instructions. These are classified as RISC chips (reduced instruction set computer), of which the PIC microcontroller is an example.

As stated above, CPU cannot work on its own; it needs some memory and input/output devices for getting data in, storing it and sending it out again. The main memory block is

(a)

Figure 1.3 PC motherboard. (a) PC motherboard in the main unit; (b) Layout of PC motherboard.

made up of RAM (read and write memory) chips, which are mounted in SIMMs (single in-line memory modules). Higher capacity DIMMs (dual in-line memory modules) are used currently. These can be seen at the top of the photograph in Fig. 1.3(a). Additional peripheral interfacing boards are fitted in the expansion card slots to connect the main board to the disk drives, VDU, printer and network. Spare slots allow additional peripheral interfaces and more memory to be added if required. Each peripheral interface is a sub-circuit which is built around a specific input/output chip (or set of chips) which handles the data transfer.

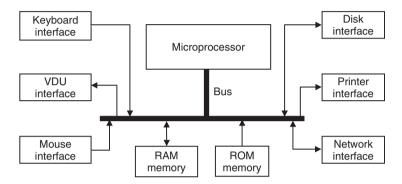

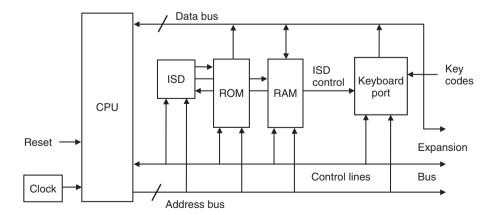

The integrated support device (ISD) is a chip which provides various system control and memory management functions in one chip, and is designed for that particular motherboard. The motherboard itself can be represented as a block diagram (Fig. 1.4) to show how the components are interconnected.

Figure 1.4 Block diagram of PC motherboard.

The block diagram shows that the CPU is connected to the peripheral interfaces by a set of bus lines. These are groups of connections on the motherboard which work together to transfer the data from the inputs, such as keyboard, to the processor, and from the processor to memory. When the data has been processed and stored, it can be sent to an output peripheral, such as the screen. We will look at how this is achieved in more detail later.

Busses connect all the main chips in the system together, but, because they operate as shared connections, can only pass data to or from one peripheral interface or memory location at a time. This arrangement is used because separate connections to all the main chips would need an impossible number of tracks on the motherboard. The disadvantage of bus connection is that it slows down the program execution speed, because all data transfers use the same set of lines, and only one data word can be present on the bus at any one time. To help compensate for this, the bus connections are typically 16, 32 or more bits wide, that is, there are 16 or 32 connections working together, each carrying one bit of a data word simultaneously. This parallel data connection is faster than a serial connection, such as the keyboard input or network connection, which can only carry one bit at a time. In the microcontroller, these system bus connections are hidden inside the chip, making circuit design easier.

#### 1.1.3 PC Memory

There are two types of memory in the PC system. The main memory block is RAM, where input data is stored before and after processing in the CPU. The operating system and application program are also copied to RAM from disk for execution, because access to data in RAM is

faster. Unfortunately, RAM storage is 'volatile', which means that the data and application software disappear when the PC is switched off, and these have to be reloaded each time the computer is switched back on.

This means that some ROM (read only memory), which is non-volatile, is needed to get the system started at switch on. The BIOS (basic input/output system) ROM chip, seen at the left of Fig. 1.3(a), contains enough code to check the system hardware and load the main operating system (OS) software from disk. It also contains some basic hardware control routines so that the keyboard and screen can be used before the main system has been loaded.

The hard disk is a non-volatile, read/write storage device, consisting of a set of metal disks with a magnetic recording surface, read/write heads, motors and control hardware. It provides a large volume of data storage for the operating system, application and user files. A number of applications can be stored on disk and then selected as required for loading into memory; because the disk is read and write device, user files can be stored, applications added and software updates easily installed.

#### 1.2 Wordprocessor Operation

In order to understand the operation of the PC microprocessor system, we will look at how the wordprocessor application uses the hardware and software resources.

#### 1.2.1 Starting the Computer

When the PC is switched on, the BIOS ROM program starts automatically. It checks that the system hardware is working properly and displays messages to report the results. If there is a problem, the BIOS program attempts to diagnose the fault, and will display an error message. If all is well, it loads (copies) the main operating system software (Windows) from hard disk into RAM. As you will probably have noticed, this all takes some time; this is an indication of the amount of data transfer required, and the relatively slow access to the hard drive.

#### 1.2.2 Starting the Application

Windows displays an initial screen with icons and menus which allows the application to be selected using the mouse and on-screen pointer. Word is started by clicking on its icon; Windows converts this action to a command which runs the executable file (WINWORD.EXE) stored on disk. In older machines the operating system, MSDOS (Microsoft disk operating system), required this command to be typed in to start the application.

The application program is transferred from disk to RAM, or as much of it as will fit in the available memory. If necessary, application program blocks can be swapped into memory when needed. The wordprocessor screen is displayed and a new document file can be created or an existing one loaded by the user from disk for updating.

#### 1.2.3 Data Input

The main data input is obviously from the keyboard, which consists of a grid of switches which are scanned by a dedicated microcontroller within the keyboard unit. This chip detects when a key has been pressed, and sends a corresponding code to the CPU via a serial data line in the keyboard cable. The serial data is a sequence of high and low voltages on a single wire,

which represent a binary code, each key generating a different code. The keyboard interface converts this serial code to parallel form for transfer to the CPU via the system data bus. It also signals separately to the CPU that a keycode is ready to be read into the CPU, by generating an 'interrupt' signal. This serial-to-parallel (or parallel-to-serial) data conversion process is required in all the interfaces that use serial data transfer, namely, the keyboard, VDU, network and modem. Binary coding, interrupts and other such processes will be explained in more detail later.

In Windows, and other GUIs, the mouse can be used to select commands for managing the application and its data. It controls a pointer on the screen; when the mouse is moved, the ball turns two rollers, which have perforated wheels attached. The holes are detected using an opto-detector, which sends pulses representing movement in two directions. These pulse sequences are passed to the CPU via the mouse interface and used to modify the position of the pointer on the screen. The buttons, used to select an action, must also be input to the CPU.

#### 1.2.4 Data Storage

Each character of the text being typed into the wordprocessor is stored as an 8-bit (one byte) binary code, which occupies one location in RAM. Each bit of data must be stored as a charge on small capacitor in the RAM chip. The parallel data is received by the CPU, then sent back via the same data bus lines from the CPU to the RAM. The RAM stores the data bytes at numbered locations; these address numbers are identified by the CPU using the system address bus. The data is transferred on the data bus to the address in RAM selected by the CPU via the ISD, which provides the additional logic required to handle the data transfers.

#### 1.2.5 Data Processing

In the past, programs running on the DOS operating system required less processing power, partly because the screen was simpler, being divided up into one space for each character. The video interface would convert the stored character code into the pattern for the character, and output it to the correct position on the screen.

The Windows screen is more complicated, because the text is displayed in graphics (drawing) mode, at a higher resolution, so that the text size, style and layout appears on screen as it will be printed. Graphics, tables and special characters can be embedded in the text. This means the CPU has far more work to do in displaying the page, and this is one reason why Windows needs more memory and a more powerful CPU than former DOS-based wordprocessors. The processor must also manage the WIMP (Windows, Icons, Mouse, Pointer) interface, which allows actions to be selected on screen. Word now has many more features than earlier wordprocessors, and there is now little difference between a typical wordprocessor and so called desk-top publishing (DTP) programs, which provide comprehensive page layout control.

#### 1.2.6 Data Output

The characters must be displayed on the screen as they are typed in, so the character codes stored in memory are also sent to the VDU via the system data bus and video interface. The display is made up of single coloured dots (pixels) organised in lines across the screen, which are output in sequence from a video amplifier. This is known as a scanned display. The shape of the character on screen must be generated from its code in memory, and sent out on the correct set of lines at the right time on the video signal. The display is therefore formed as a two-dimensional image made up from a serial data stream which sets the colour of each pixel on the screen in turn, line by line.

If a file is transferred on a network, it must also be sent in serial form. The characters (letters) in a text file would typically be sent as ASCII code, along with formatting information and network control codes. ASCII code represents one character as one byte (8 bits) of binary code, and is therefore a very compact form of the data. The code for 'A' for example is 01000001.

The printer works in a similar way to the screen, except that the output is generated as lines of dots of ink on a page. If you watch an inkjet printer working, you can see the scanning operation take place. In older printers, the data is sent in 8-bit parallel form, along with control codes, via the printer port. If the printer itself is capable of formatting the final output, only the character code and any formatting codes are needed. For cheaper printers, the computer itself must generate the page layout, and send a 'bit-map' of the page, where one bit (or group of bits) is the code for one coloured dot on the page; this will take longer.

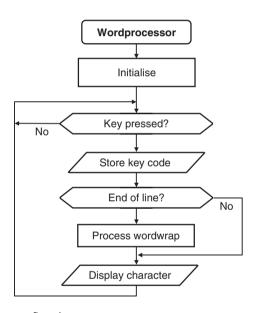

The operation of the wordprocessor can be illustrated using a flowchart, which is a graphical method of describing a sequential process. Figure 1.5 describes only the basic process of text input and word wrapping at the end of each line. Flowcharts will be used later to represent microcontroller program operation.

Figure 1.5 Wordprocessor flowchart.

#### 1.3 PC Microprocessor System

As we have seen, the PC working as a wordprocessor carries out the following functions:

- Data input

- Data storage

- Data processing

- Data output

All microprocessor systems perform these same basic functions. To carry them out, the microprocessor system needs a set of supporting chips with suitable interconnections. The system will therefore typically consist of:

- CPU

- RAM

- ROM

- I/O (Input/Output) ports

- ISD

- XTAL (crystal) clock generator

These devices must be interconnected by:

- address bus

- data bus

- · various control lines

These busses and control lines originate from the CPU, which is in overall charge of the system.

#### 1.3.1 System Operation

The PC motherboard components are connected as shown in Fig. 1.6. The address and data busses, control lines and support chip are required to handle the data transfer between the CPU, memory and ports. The clock circuit contains a crystal oscillator as found in watches and clocks, which produces a precise fixed frequency signal which drives the microprocessor. The CPU operations are triggered on the rising and falling edges of the clock signal, allowing their relative timing to be precisely controlled. This allows events in the CPU to be completed in the correct sequence, with sufficient time allowed for each step.

The CPU generates all the main control signals based on this timing reference. This is why the CPU should not be operated at a frequency above its rated clock speed – correct completion of each step can no longer be guaranteed, and the system could crash. A given CPU can be used in different system designs, depending on the type of application, the amount of memory needed, the I/O requirements and so on. The ISD is designed to assist the processor to handle memory and I/O operations within a particular design.

Figure 1.6 Block diagram of PC microprocessor system.

For simplicity, only the keyboard port is shown in the block diagram, as this was sometimes (in older designs) the only I/O device on the main board. However, other ports, such as the printer, modem and so on are connected in the same way, whether they are part of the motherboard or fitted as expansion cards. The signal connections to the plug-in peripheral interfaces will be made to the system busses and the relevant control lines via the expansion bus, which appears on the motherboard as edge connectors. This allows the system to be upgraded by replacing or adding to these cards. In current designs, where upgrading is less likely to be required, the VDU, disk and network tend to be integrated onto the main board. Additional RAM memory may be fitted in a similar way if spare slots are available.

#### 1.3.2 Program Execution

The ROM and RAM memory contain program information and data in numbered locations. The ISD contains address decoding logic which allocates a particular memory chip to a range of addresses. The I/O port registers, which are set up to handle the data transfer in and out of the system, are also allocated particular addresses by the system designer, and accessed by the CPU in the same way as memory locations.

A register is a temporary store for a data word within a port chip or the CPU. In the port chip it can hold data, or a control code which sets up how the port will operate. For example, the bits in the data direction register control whether each port pin operates as an input or an output. The data being sent in or out is then stored temporarily in the port data register. More of this later!

The wordprocessor program consists of a list of instructions in binary code stored in memory, with each instruction and any associated data (operands) being stored in sequential locations. The program instruction codes are fetched into the CPU and decoded. The CPU sets up the internal and external control lines as necessary and carries out the operation specified in the program, such as read a character code from the keyboard port into the CPU. The instructions are executed in order of their addresses, unless the instruction itself causes a jump to another point in the program, or an interrupt is received.

#### 1.3.3 Execution Cycle

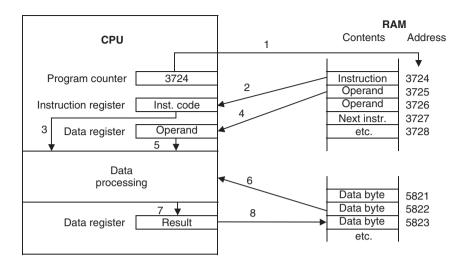

Program execution is illustrated in Fig. 1.7. Assuming that the application program code is in RAM, the program execution cycle proceeds as follows:

- The CPU outputs (1) the address of the location (memory slot) containing the required instruction. This address is kept in the program counter. The sample address is shown in decimal (3724) in Fig. 1.7, but it is output in binary form on the address lines from the processor. The ISD uses the address to select the RAM chip which has been allocated to this address. The address bus also connects directly to the RAM chip to select the individual location.

- 2. The instruction code is returned to the CPU from the RAM chip via the data bus (2). The CPU reads the instruction from the data bus into an instruction register. The CPU then decodes and executes the instruction (3). The operands (data to be processed) are fetched (4) from the following locations in RAM via the data bus, in the same way as the instruction.

- 3. The instruction execution continues by feeding the operand(s) to the data processing logic (5). Additional data can be fetched from memory (6) (this would be the text data in our

**Figure 1.7** Program execution sequence.

wordprocessor). The result of the operation is stored in a data register (7), and then, if necessary, in memory (8) for later use. In the meantime, the program counter has been incremented (increased) to the address of the next instruction code. The address of the next instruction is then output and the sequence repeats from step 2.

The operating system, the wordprocessor program and the text data are stored in different parts of RAM during program execution, and the wordprocessing application program calls up operating system routines as required to read in, process and store the text data. Current CISC processors such as the Pentium series have instructions which are more than 8 bits in size which are stored in multiple locations, and use complex memory management techniques, to speed up program execution. These long instructions and data words are normally multiples of 8 bits, as this is how the memory is organised.

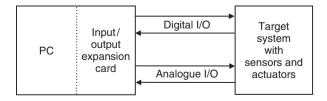

#### 1.4 PC Engineering Applications

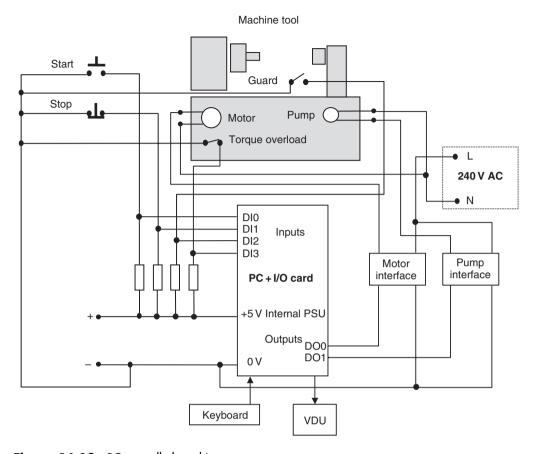

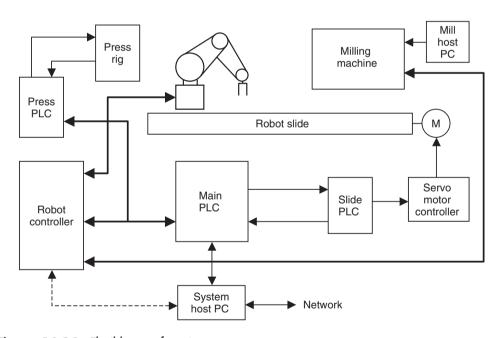

The PC can be used as a standard hardware platform in a variety of engineering systems by fitting special interfacing hardware in the expansion slots and programming the PC to control the target system through this I/O hardware (Fig. 1.8). This type of arrangement is increasingly used in manufacturing systems where the PC might control a machine tool, robot or assembly system, or be used to run an instrumentation or data logging application. The PC provides a

Figure 1.8 PC engineering application.

standard network interface so that commands or design data can be sent to the PC and status information and other measurement data can be returned to a supervisory computer.

The PC has the advantage of using a standard operating system and programming languages which allow control programs to be written in high level languages such as 'C' or Visual Basic. Graphical programming tools are also available for designing control and instrumentation applications more quickly and easily. An example of this type of system is given in Chapter 16.

#### 1.5 The Microcontroller

We have now looked at some of the main ideas to be used later in explaining microcontroller operation: hardware, software, how they interact and how the function of complex systems can be represented in a simplified form such as block diagrams and flowcharts. We can now compare the PC system with an equivalent microcontroller system.

The microcontroller can provide, in a simplified form, all the main elements of the conventional microprocessor system on a single chip. As a result, less complex applications can be designed and built quickly and cheaply. A working system can consist of a microcontroller chip and just a few external components for feeding data and control signals in and out.

#### 1.5.1 A Microcontroller Application

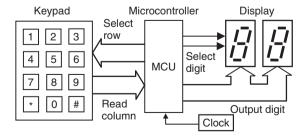

A simple equivalent of the word processing application described above could be built as shown in Fig. 1.9, around an MCU (microcontroller unit).

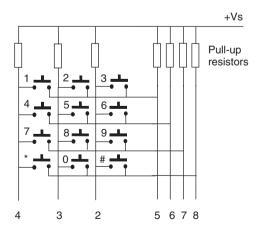

The basic function of the system shown is to store and display numbers which are input on the keypad. The microcontroller chip can be programmed to scan the keypad and identify any key which has been pressed. The keys are connected in a  $3 \times 4$  grid of rows and columns, so that a row and a column are connected together when the key is pressed. The microcontroller can identify the key by selecting a row and checking the columns for a connection. Thus, four input lines and three outputs are required for connection to the microcontroller. In order to simplify the drawing, these parallel connections are represented by the block arrows.

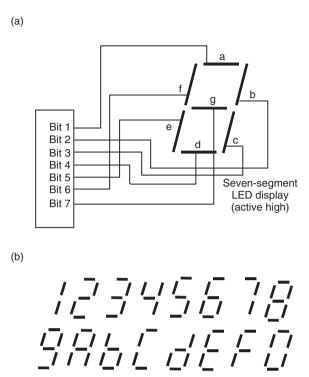

Seven-segment displays show the input numbers as they are stored in the microcontroller. Each display digit consists of seven light emitting diodes (LEDs) which show as a line segment of the number when lit. Each number from 0 to 9 is displayed as a suitable pattern of lit segments.

Figure 1.9 Microcontroller keypad display system.

The basic display program could work as follows: when a key is pressed, the digit is displayed on the right (least significant) digit, and subsequent keystrokes will cause the previously entered digit to shift to the left, to allow decimal numbers up to 99 to be stored and displayed. Calculations could then be performed on the data, and the result displayed.

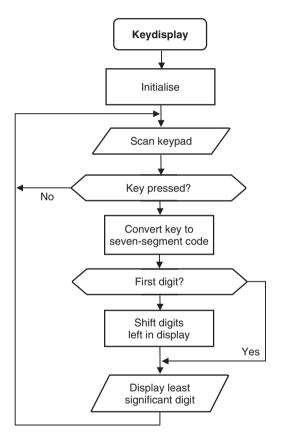

The starting point for writing the program for the microcontroller is to convert the general description given above into a description of the operations which can be programmed into the chip using the set of instructions which are available for that microcontroller. The instruction set is defined by the manufacturer of the device. The process whereby the required function is implemented is called the program algorithm, which can be graphically represented by a flowchart (Fig. 1.10).

Figure 1.10 Flowchart for keypad display program.

With suitable development of the software and/or hardware, the system could be modified to work as a calculator, message display, electronic lock or similar application. Additional digits could be added to the display as required. Keyboard scanning and display driving are standard operations for microcontrollers, and the techniques required to create the working application will be explained in later chapters.

#### 1.5.2 Programming a Microcontroller

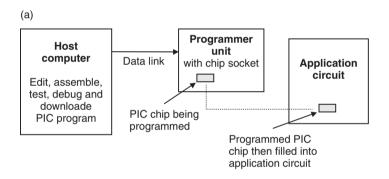

Some microcontrollers have ROM program memory, which is programmed before the chip is fitted into the application circuit, and cannot be changed. One-time programmable (OTP) devices are generally used for longer production runs where the program is known to be correct. We will be using PIC chips which have flash program memory, which can be erased and re-programmed many times, which is invaluable when learning. A PIC device is programmed by placing it in a special programming unit which is attached to a host computer (Fig. 1.11). Note the zero insertion force (ZIF) socket which will accept different-sized chips for programming.

The program is written and converted to machine code in the host computer using suitable development system software and downloaded via a serial data link to the chip in the programmer unit. The microcontroller is then taken out of the programmer, and placed in the application circuit. The circuit can then be checked for correct operation.

Having introduced some basic ideas concerning microprocessors and microcontrollers, in the next chapter we will review some principles of digital circuits and microprocessor systems. The process of creating microcontroller applications such as the example outlined above can then be tackled.

(b)

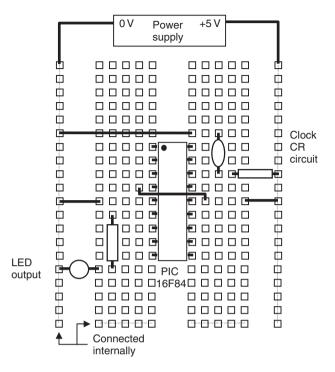

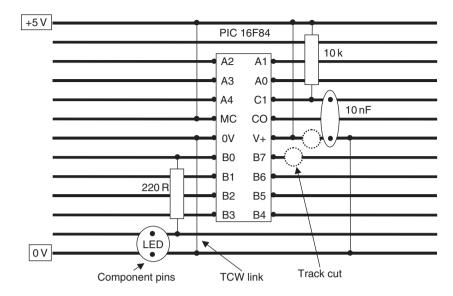

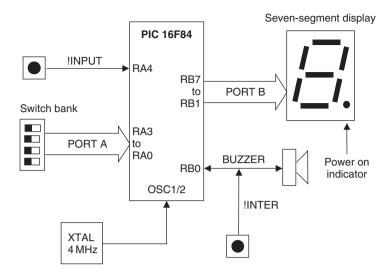

**Figure 1.11** Programming a PIC microcontroller. (a) PIC program downloading; (b) PIC programming unit.

#### Summary

- The PC consists of data input, storage, processing and output devices.

- The main unit is a modular system, consisting of the motherboard, power supply, disk drives and expansion cards containing interfacing circuits plugged into the motherboard.

- The motherboard carries the microprocessor (CPU) chip, RAM memory modules, a BIOS ROM, ISD and keyboard interface.

- The CPU communicates with the main system chips via a shared set of address and data bus lines. The address lines select the device and location for the data to be transferred on the data bus.

- The microcontroller provides, in simplified from, most of the features of a conventional microprocessor system on one chip.

#### Questions

- 1. Name at least two PC input devices, two output devices and two storage devices.

- 2. Why is the BIOS ROM needed when starting the PC?

- 3. Why are shared bus connections used in the typical microprocessor system, even though it slows down the program execution?

- 4. State two advantages of the modular PC hardware design.

- 5. Why does the PC take so long to start up?

- 6. Sort these data paths into serial and parallel:

- (a) internal data bus

- (b) keyboard input

- (c) VDU output

- (d) printer output

- (e) modem I/O

- 7. State the function, in ten words or less, of the:

- (a) CPU

- (b) ROM

- (c) RAM

- (d) ISD

- (e) address bus

- (f) data bus

- (g) program counter

- (h) instruction register

- 8. Explain the difference between a typical microprocessor and microcontroller.

#### Activities

- 1. Study the messages which appear on the screen when PC is switched on, and explain their significance with reference to the system operation.

- 2. Under supervision if necessary, and with reference to relevant manuals, carry out the following investigation: Disconnect the power supply and remove the cover of the main unit of a PC and identify the main hardware subsystems power supply, motherboard and disk units. On the motherboard, identify the CPU, RAM modules, expansion slots, keyboard interface, VDU interface, disk interface, printer interface. Is there an internal modem or network card? Are there any other interfaces fitted?

- 3. Run the wordprocessor and study the process of word-wrapping which occurs at the end of each line. Describe the algorithm that determines the word placement, and the significance of the space character in this process. Draw a flowchart to represent this process.

## **Chapter 2**Information Coding

- 2.1 Number Systems

- 2.2 Machine Code Programs

- 2.3 ASCII Code

This chapter introduces some methods for representing information within microprocessor systems. Binary and hexadecimal number systems will be outlined, so that data storage and program coding methods can be explained.

Much of modern technology is based on the use of mathematical models to represent information and processes in the real world. These mathematical models are used in engineering to help design new systems and products. For instance, the three-dimensional drawing of a suspension arm for a car created on a CAD (computer aided design) system screen is generated from a digital representation of the shape of the part in the memory of the computer. The advantages of the computer model are fairly obvious – it can be stored on disk, transferred electronically and modified much more easily than the equivalent information on paper. The component design can also be mathematically analysed in the computer prior to construction. For example, the stresses and strains to which the component will be subject at its final position in the suspension assembly can be studied. Further, when a component design is finished, the design data can be converted directly to a program for a machine tool which will automatically manufacture the part.

The programs for our microcontroller applications will be stored in the same way; we therefore need to know something about how such data is represented in the computer.

#### 2.1 Number Systems

Mathematics is based on number systems, which use a set of characters to represent numerical values. The characters used are simply symbols, just squiggles on a page, but the number systems they are part of have been developed over thousands of years – because they are so useful.

In microprocessor, microcontroller and digital electronic systems, numerical processing is carried out using binary codes, a number system which has only come into common use with the development of digital computers. We therefore have to understand binary numbering in order to use a microcontroller. Another number system, hexadecimal, is also useful here because it provides a more compact way of representing binary code.

# 2.1.1 Decimal: Base 10

The name of each number system refers to the 'base' of the number system, which corresponds to the number of symbols used in representing values. In decimal, ten symbols are used, with which, hopefully, you are familiar:

) 1 2 3 4 5 6 7 8 9

Why use a particular base number? The reason for using ten is simple – we humans have ten fingers which can be used for counting, so the decimal system was developed as a way of writing this down and doing calculations on paper (or stone!) instead of on our fingers. We use the term 'digit' to refer to fingers and numbers and 'digital' to describe binary electrical circuits. The use of written numbers was essential for the original development of industry and commerce.

Assuming that we know how to count and write down numbers in decimal, let's analyse what a typical number means. Take the number 274; in words, it is two hundred and seventy four. This means: take two hundreds, seven tens and four units and add them together. The position of each digit in the number is literally significant; each column has a weighting which applies to the digit in that column. As you know, the least significant digit is conventionally placed at the right, and the most significant at the left. More digits are added at the left hand end as the number size increases. In decimal, the columns have a weight 1, 10, 100, etc. Note that these correspond to a power series of 10, the number system base. Another example is detailed in Table 2.1.

A number system can be used with any base you like, but some are more useful than others. For instance, relics of the base 12 system are still in use – think of clocks, boxes of eggs and measurement of angles. Base 12 is useful because 12 is divisible by 2, 3, 4 and 6, giving lots of useful fractions – a half, a third, a quarter and one-sixth. However, the decimal system is our standard system, so the analysis of other systems will still be based on decimal for comparison of number values.

# 2.1.2 Binary: Base 2

Binary is used in digital computer systems because it represents the way that values are stored and processed. The binary digits, 0 and 1, represent two voltage levels used in digital circuits, typically 5 V and 0 V. We can understand the binary system by comparing it with decimal – the basic rules are the same for any number system.

In binary, the base is 2, so the column weighting is a power series of 2, as shown in Table 2.2 (note that any number to the power zero has the value 1). With a base of 2, only the digits

| Column weight | 1000            | 100             | 10              | 1   |

|---------------|-----------------|-----------------|-----------------|-----|

| Power of base | 10 <sup>3</sup> | 10 <sup>2</sup> | 10 <sup>1</sup> | 100 |

|               |                 |                 |                 |     |

| Digits        | 3               | 6               | 5               | 2   |

**Table 2.1** Structure of a decimal number

**Table 2.2** Structure of a binary number

Least significant bit (LSB) ¬ Most significant bit (MSB) - $2^{7}$ 26  $2^{5}$  $2^{4}$  $2^3$  $2^2$  $2^1$  $2^{0}$ Column weight Decimal weight 128 64 32 16 8 4 2 1 Example number 0 0 0 0 1 1 1 1 Decimal equivalent 128 + 0 + 32 + 0 + 0 + 0 + 2 + 1 = 163

0 and 1 are available, so the numbers tend to have lots of digits. For instance, a 32-bit computer uses 32-digit binary numbers. An example with 8 digits is given showing what the digits represent and how to convert the value back to decimal.

The decimal equivalent in all number systems can be calculated by multiplying the digit value by its weighting in decimal, and then adding the resulting column products. In binary, because the digit value is 1 or 0, the result can be obtained by simply adding the digit weight where the digit value is a '1', because any number multiplied by zero is zero. When decimal data is entered into a computer, the values are converted to binary. The program instructions which process input and output data are also stored as binary codes.

# 2.1.3 Hexadecimal: Base 16

Binary numbers have lots of digits, so they are not very easy to understand when written down or printed out. Conversion to decimal is not particularly straightforward, so hexadecimal is used as a way to represent binary numbers in a compact way, while allowing easy conversion back to the original binary.

Hexadecimal (base 16), or 'hex' for short, uses the same digits as the decimal system from 0 to 9, then uses letters A to F, as a single character representation for numbers 10–15. Thus, characters which are normally used to make words, are here used as numbers, because the symbols are already available. A binary number can then be easily converted to hex by writing it down in groups of 4 bits, and then converting each group to its equivalent hex digit, as in Table 2.3.

The base of the number can be shown as a subscript where necessary to avoid confusion. All number systems use the same set of characters, so if the base of the number given is not obvious from the context, it can be specified. For example, the number 100 (one, zero, zero) could have the decimal value 4 in binary, 100 (one hundred) in decimal or 256 in hexadecimal. A letter following a number can also indicate its base, such as A9h for hexadecimal. Later, we will see other ways of indicating numerical type when programming.

Some examples of equivalent values are given in Table 2.4. The numbers are printed in 'Courier' type, as used on old-fashioned typewriters, because each character occupies the same space, so all the digits line up neatly in columns.

# 2.1.4 Counting

A list of equivalent numbers, counting from zero, is given in Table 2.5, with some comments on important values. This table also defines memory capacity in microprocessor systems; for example, '1k' of memory is 1024 locations. Notice that  $1024 = 2^{10}$ . This is worth remembering as a starting point in calculating memory capacity.

Table 2.3

Hexadecimal digits

| Decimal | Binary | Hexadecimal |

|---------|--------|-------------|

| 0       | 0000   | 0           |

| 1       | 0001   | 1           |

| 2       | 0010   | 2           |

| 3       | 0011   | 3           |

| 4       | 0100   | 4           |

| 5       | 0101   | 5           |

| 6       | 0110   | 6           |

| 7       | 0111   | 7           |

| 8       | 1000   | 8           |

| 9       | 1001   | 9           |

| 10      | 1010   | A           |

| 11      | 1011   | В           |

| 12      | 1100   | C           |

| 13      | 1101   | D           |

| 14      | 1110   | E           |

| 15      | 1111   | F           |

Table 2.4

Examples of equivalent values

| Decimal                                                               | Binary                                                                                                                    | Hexadecimal                                                       |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| $16_{10} \\ 31_{10} \\ 100_{10} \\ 169_{10} \\ 255_{10} \\ 1024_{10}$ | $\begin{array}{c} 1\ 0000_2 \\ 1\ 1111_2 \\ 110\ 0100_2 \\ 1010\ 1001_2 \\ 1111\ 1111_2 \\ 100\ 0000\ 0000_2 \end{array}$ | $10_{16} \\ 1F_{16} \\ 64_{16} \\ A9_{16} \\ FF_{16} \\ 400_{16}$ |

Table 2.5

Significant equivalent numbers

| Decimal<br>(Base 10)                           | Binary<br>(Base 2)                                                     | Hex<br>(Base 16)                                         | Comment                                                                                                                                                                                                       |

|------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 0<br>1<br>10<br>11<br>100<br>101<br>110<br>111<br>1000<br>1001<br>1010 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B | All the same All the same [2¹] Use 2nd column in binary Maximum 2-bit count [2²] Use 3rd column in binary  Maximum 3-bit count [2³] Use 4th column in binary  Decimal and hex same until 9 Use letters in hex |

| 12                                             | 1100                                                                   | C                                                        |                                                                                                                                                                                                               |

| 13                                             | 1101                                                                   | D                                                        |                                                                                                                                                                                                               |

|                                                |                                                                        |                                                          | continued                                                                                                                                                                                                     |

Table 2.5 continued

| Decimal<br>(Base 10) | Binary<br>(Base 2)                      | Hex<br>(Base 16) | Comment                                 |

|----------------------|-----------------------------------------|------------------|-----------------------------------------|

| 14                   | 1110                                    | E                |                                         |

| 15                   | 1111                                    | F                | Maximum 4-bit count                     |

| 16                   | 1 0000                                  | 10               | [2 <sup>4</sup> ] Use 2nd column in hex |

| 17                   | 1 0001                                  | 11               | Use space to clarify binary             |

| 18                   | 1 0010                                  | 12               |                                         |

| 19                   | 1 0011                                  | 13               |                                         |

| 20                   | 1 0100                                  | 14               |                                         |

| 21                   | 1 0101                                  | 15               |                                         |

| 22                   | 1 0110                                  | 16               |                                         |

| 23                   | 1 0111                                  | 17               |                                         |

| 24                   | 1 1000                                  | 18               |                                         |

| 25<br>26             | 1 1001                                  | 19<br>1A         |                                         |

| 27                   | 1 1010<br>1 1011                        | 1B               |                                         |

| 28                   | 1 1100                                  | 1D               |                                         |

| 29                   | 1 1101                                  | 1D               |                                         |

| 30                   | 1 1110                                  | 1E               |                                         |

| 31                   | 1 1111                                  | 1F               | Maximum 5-bit count                     |

| 32                   | 10 0000                                 | 20               | [2 <sup>5</sup> ]                       |

| 33                   | 10 0001                                 | 21               | [2]                                     |

| 34                   | 10 0010                                 | 22               |                                         |

|                      | • • • • •                               |                  |                                         |

| 62                   | 11 1110                                 | 38               |                                         |

| 63                   | 11 1111                                 | 39               | Maximum 6-bit count                     |

| 64                   | 100 0000                                | 40               | [26]                                    |

| 65                   | 100 0001                                | 41               |                                         |

|                      |                                         |                  |                                         |

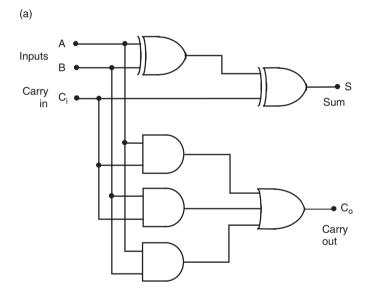

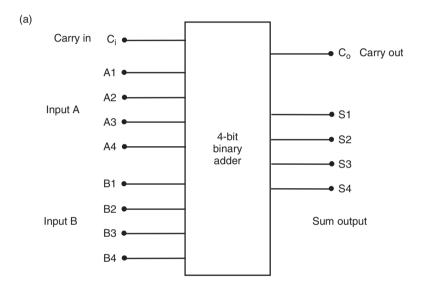

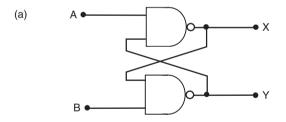

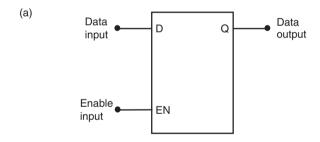

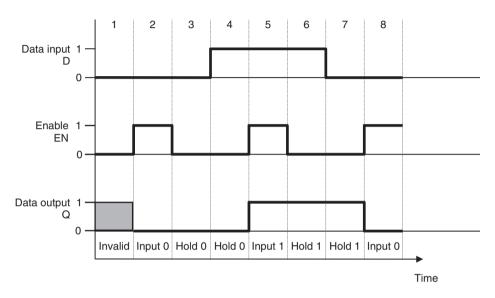

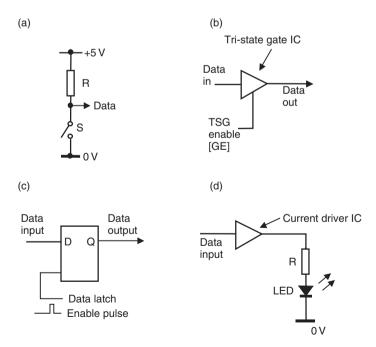

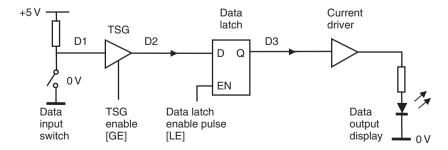

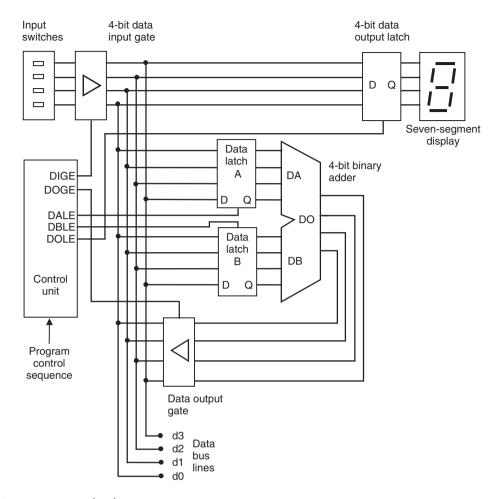

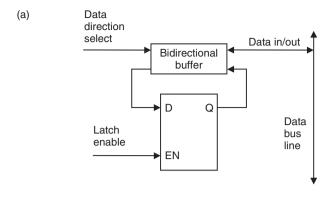

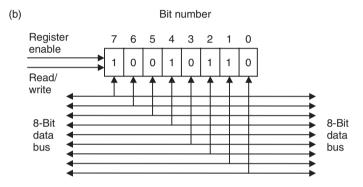

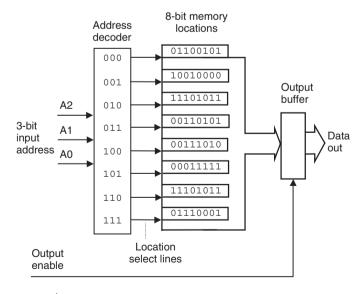

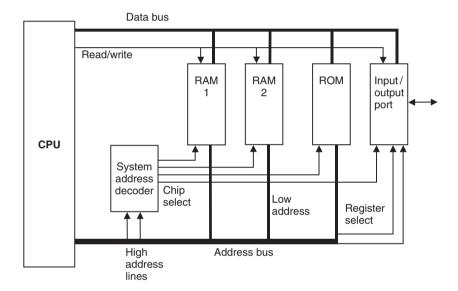

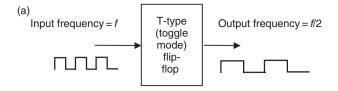

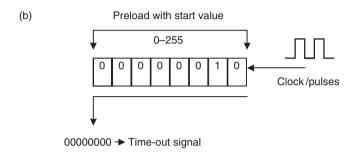

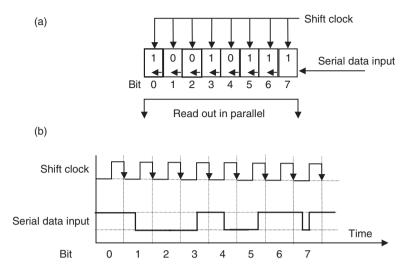

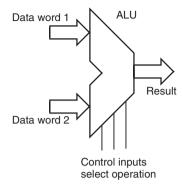

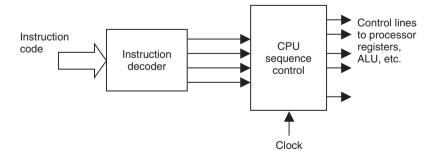

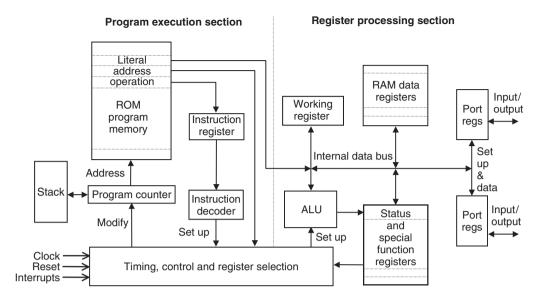

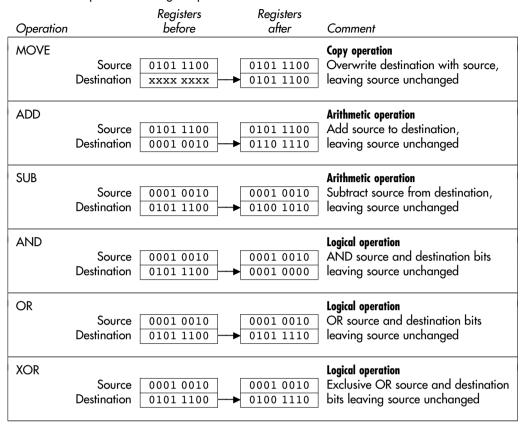

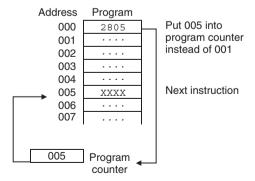

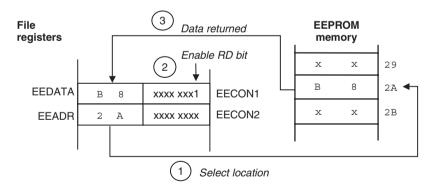

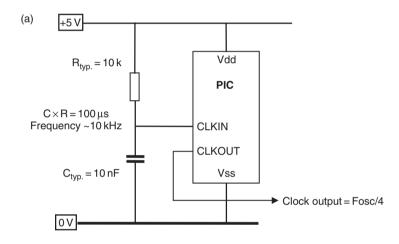

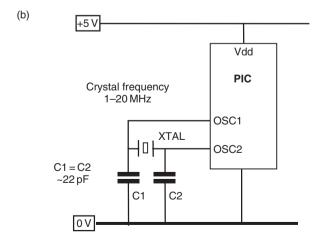

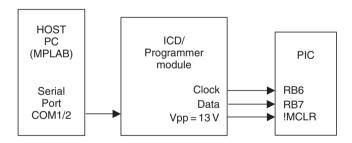

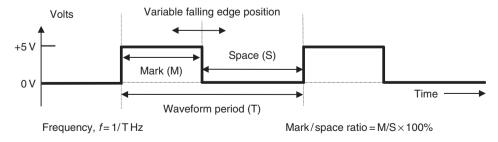

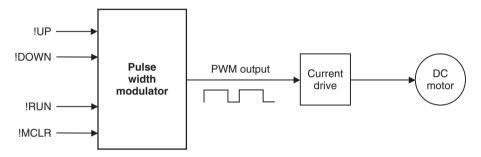

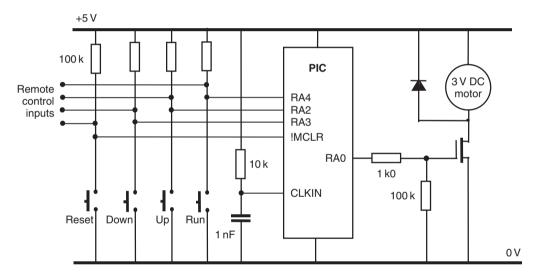

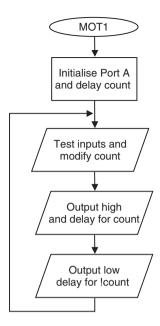

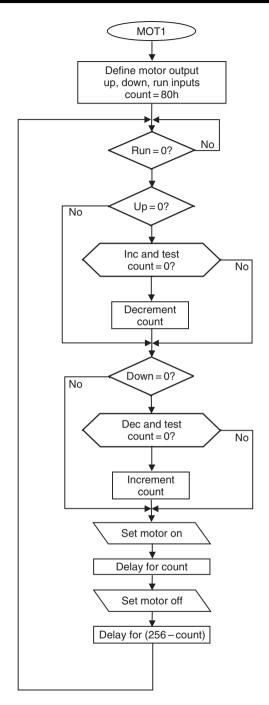

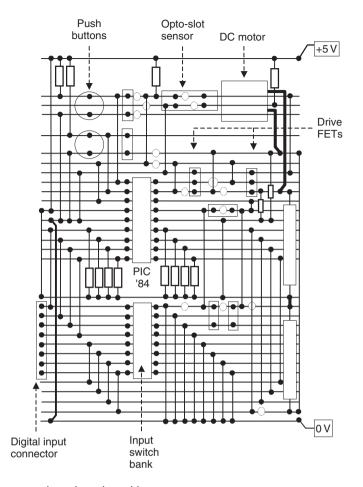

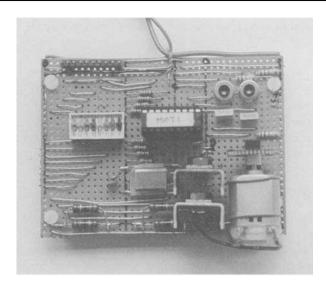

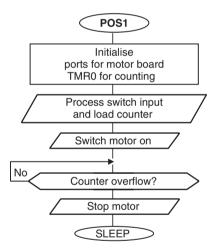

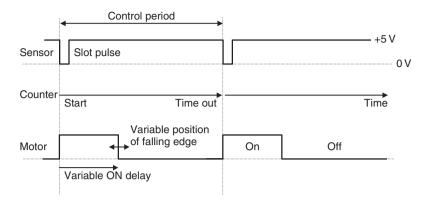

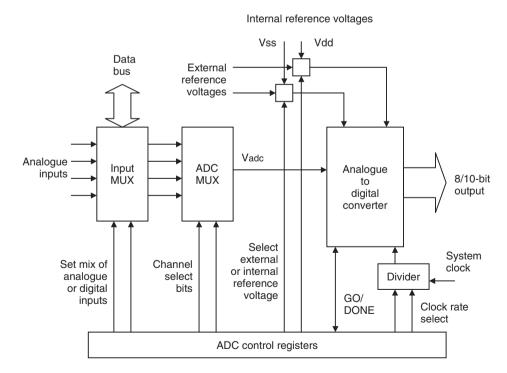

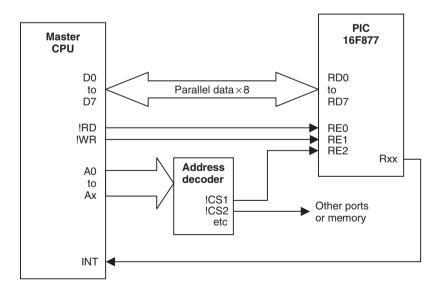

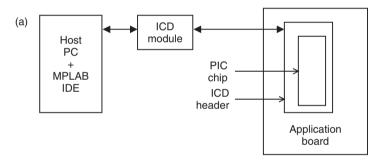

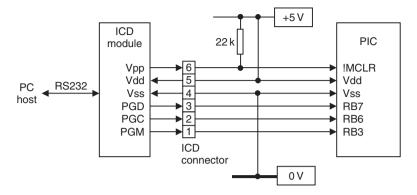

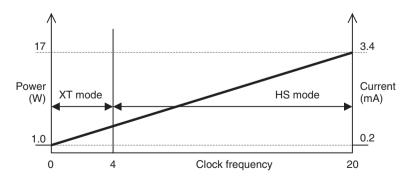

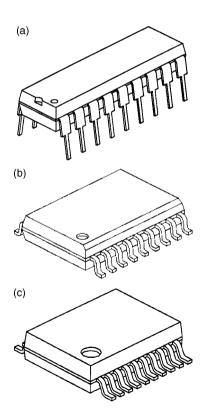

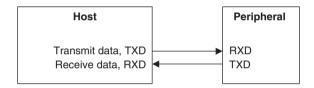

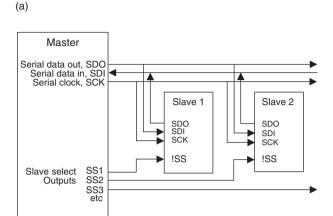

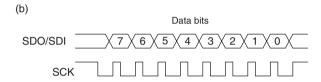

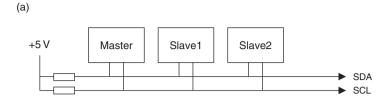

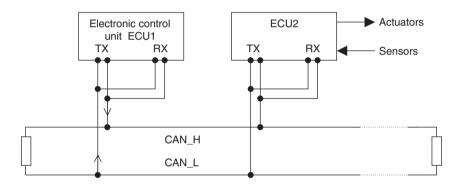

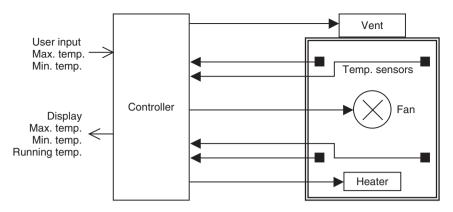

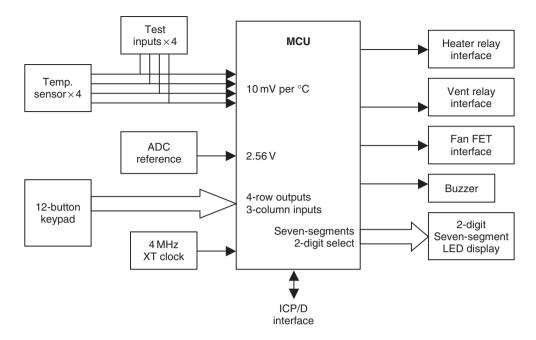

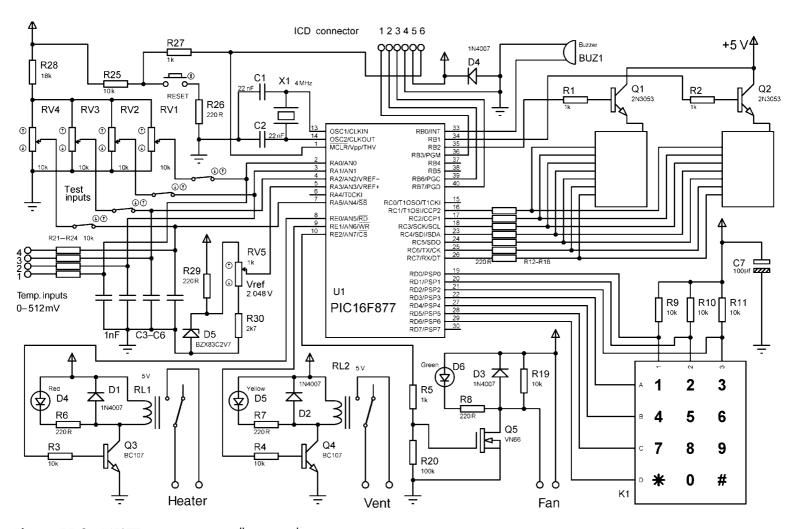

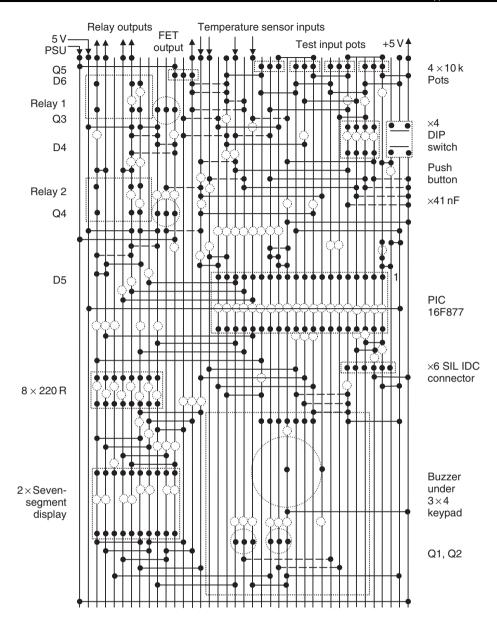

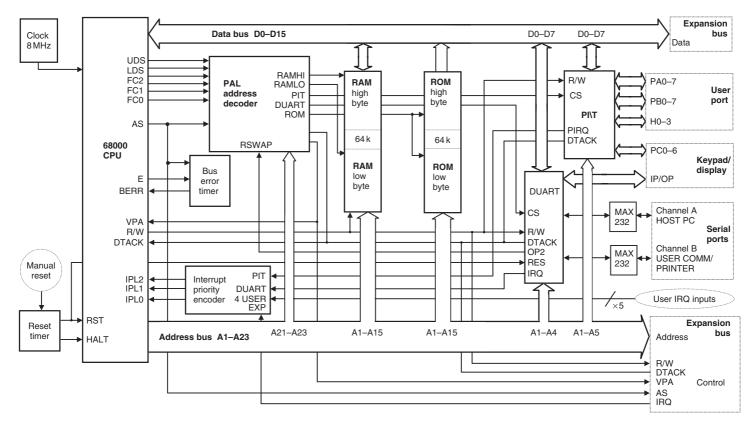

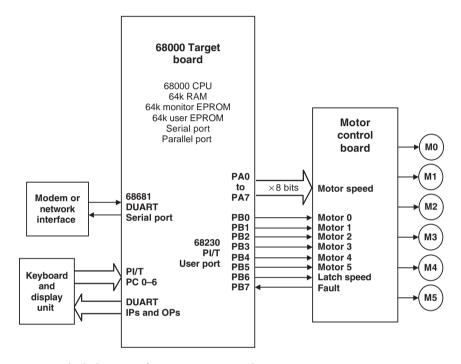

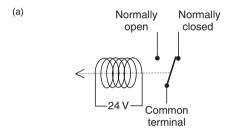

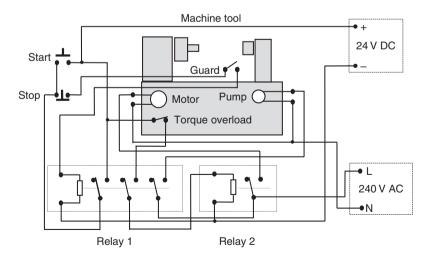

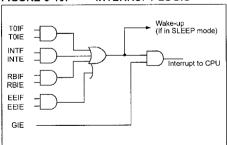

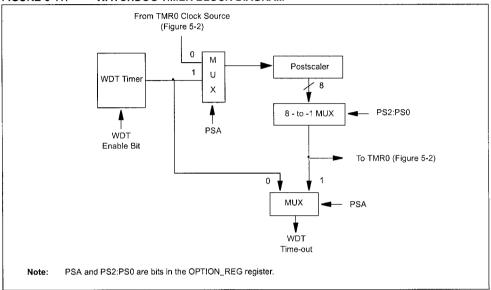

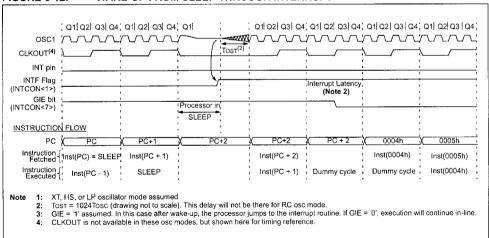

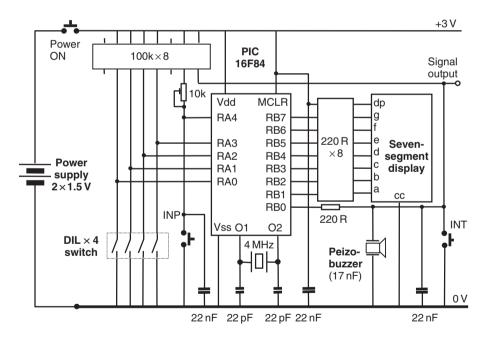

| 127                  | 111 1111                                | 79               | Maximum 7-bit count                     |